# **Investigating The Limits of Instruction Level Parallelism**

Richard D. Potter

Division of Computer Science,

University of Hertfordshire,

College Lane,

Hatfield,

Herts. AL10 9AB

email: comrrdp@herts.ac.uk

Technical Report No. 245 February 1996

#### **Abstract**

High performance computer architectures increasingly use compile-time instruction scheduling to reorder code to expose parallelism that can be exploited at run-time. Although respectable performance increases have been reported, there is still a significant performance gap between what has been achieved and what has theoretically been shown to be possible. All scheduling algorithms used to reorder code, either explicitly or implicitly introduce barriers to code motion, which in turn limit the performance realised. Trace driven simulation is used to quantify the amount of instruction level parallelism available in general purpose code and the impact of various artificial barriers to code motion. This work is based on the Hatfield Superscalar Architecture, a progressive multiple instruction issue processor. The results of this study will be used to direct future developments in instruction scheduling technology.

**Keywords**: Superscalar, Instruction-Level Parallelism, Instruction Scheduling, HSA, Trace Driven Simulation.

# **Table of Contents**

| 1. | Introduction                                    | . 1        |   |

|----|-------------------------------------------------|------------|---|

| 2. | This Study and Previous Work                    | . 1        |   |

| 3. | Hatfield Superscalar Architecture               | 3          |   |

| ٠. | 3.1 A Generalised Delayed Branch                | 1          |   |

|    | 3.2 In-order Instruction Issue                  | . T        |   |

|    | 3.3 A Common Pool of Functional Units.          | .+<br>1    |   |

|    | 3.4 Full Floating-Point Capability.             | .4         |   |

|    | 3.5 Guarded Instruction Execution.              | .5         |   |

|    | 3.6 Speculative instruction execution.          | . 5        |   |

|    | 3.0 Speculative histraction execution.          | . 3        |   |

| 4. | Limits To Instruction-Level Parallelism         | .5         |   |

|    | 4.1 Data Dependencies                           |            |   |

|    | 4.2 Control Dependencies                        |            |   |

|    | 4.3 Artificial Limitations To Code Motion       |            |   |

|    | 4.3.1 Loops                                     |            |   |

|    | 4.3.2 Procedure Call and Returns                | . 8        |   |

|    | 4.3.3 Memory Dependencies                       |            |   |

|    |                                                 |            |   |

| 5. | Trace Driven Simulation                         |            |   |

|    | 5.1 Overview of Simulator Model                 |            |   |

|    | 5.2 Representing Programs Within TDS            |            |   |

|    | 5.2.1 Principle Parameters                      |            |   |

|    | 5.3 Loading the TDS Tool                        |            |   |

|    | 5.3.1 Loading The Instructions                  |            |   |

|    | 5.3.2 Data Items                                |            |   |

|    | 5.4 Main Simulation Loop                        |            |   |

|    | 5.4.1 Trace Files                               | . 10       | ĺ |

|    | 5.4.2 Simulating the 'Execution' of a Benchmark |            |   |

|    | 5.4.3 Ceilings and Breakpoints                  | . 12       | 2 |

| 6  | Results                                         | . 13       | 2 |

|    | 6.1 Benchmark Programs                          |            |   |

|    | 6.1.1 Composition of the Benchmarks             |            |   |

|    | 6.1.2 Branch Instruction Profile                |            |   |

|    | 6.1.3 Basic Block Statistics                    |            |   |

|    | 6.2 Oracle Base Model                           |            |   |

|    | 6.3 Procedure Call and Returns                  |            |   |

|    | 6.3.1 Procedure Inlining                        |            |   |

|    | 6.3.2 Direct Recursion Inlining                 |            |   |

|    | 6.4 Effect of Loop Ceilings                     |            |   |

|    | 6.4.1 Loop Construct Removal                    | · 1.       | 1 |

|    | 6.5 Memory                                      | . Z.       | 7 |

|    | 6.5.1 Memory Disambiguation                     | 22         | ) |

|    | 6.5.2 Speculative Writes                        |            |   |

|    | 6.6 Instruction Latencies                       |            |   |

|    | 6.6.1 Adjusting Instruction Set Latencies       | ・∠⁴<br>つ・  | 1 |

|    | 6.6.2 Minimum Division                          | 24.<br>ارد | 1 |

|    | 6.7 Instruction Combining                       |            |   |

|    | 6.8 Distributions of Parallelism                | .∠(<br>״י  | - |

|    | o.o Distributions of Latanonsill                | . 4        | / |

| 7. | Conclusions and Future Work                     | .29        | 3 |

|    |                                                 |            |   |

| Q  | Pafaranaas                                      | 0          | 1 |

# **List Of Figures**

| Figure 4.1  | Read After Write Dependency.                                                                                                                             | 6  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.2  | Write After Read Dependency.                                                                                                                             | 6  |

| Figure 4.3  | Write After Write Dependency.                                                                                                                            | 6  |

| Figure 4.4  | HSA Memory Reference                                                                                                                                     | 8  |

| Figure 5.1  | Flowchart of Trace Driven Simulation                                                                                                                     | 9  |

| Figure 5.2  | Sample Breakpoint File From permcd                                                                                                                       | 10 |

| Figure 5.3  | An example section of a trace file                                                                                                                       | 12 |

| Figure 6.1  | Distribution of Branch Types and Branch Taken Figures.                                                                                                   | 15 |

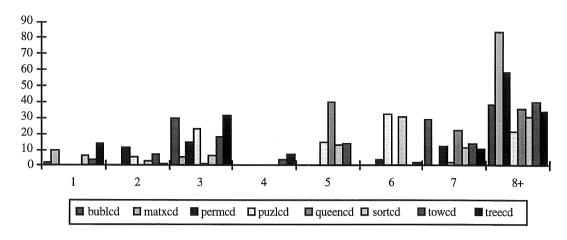

| Figure 6.2  | Dynamic Run Length Distribution of Taken Branches                                                                                                        | 16 |

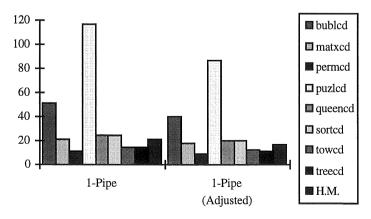

| Figure 6.3  | Oracle Base Model Results                                                                                                                                | 16 |

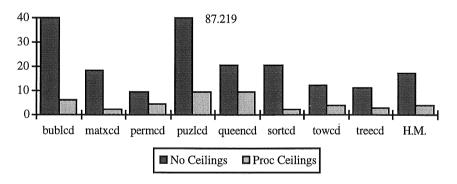

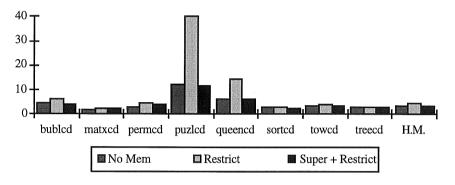

| Figure 6.4  | Effect of Ceilings on Procedure Call & Return.                                                                                                           | 17 |

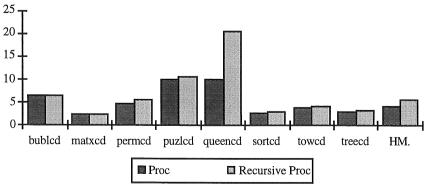

| Figure 6.5  | Effect of Procedure Inlining                                                                                                                             | 18 |

| Figure 6.6  | Inlined Recursive Procedure Calls                                                                                                                        | 18 |

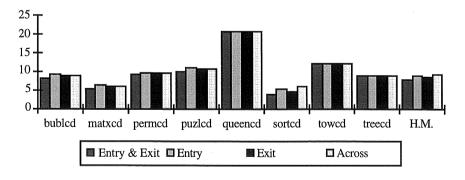

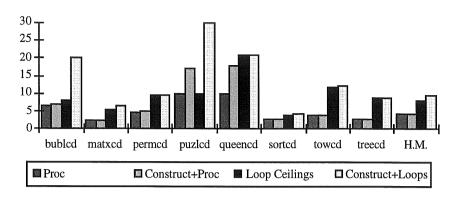

| Figure 6.7  | Effect of Loop Ceilings On Code                                                                                                                          | 19 |

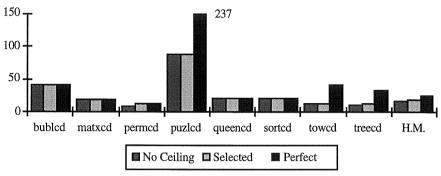

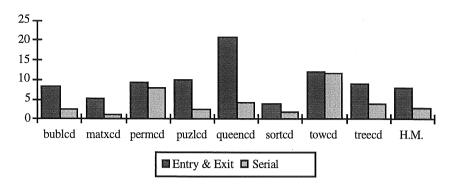

| Figure 6.8  | Effect of Serialising All Loops                                                                                                                          | 21 |

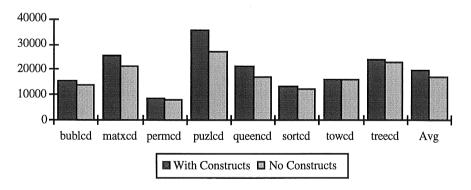

| Figure 6.9  | Instruction Exec. Counts For Benchmark and After Loop Construct Removal.                                                                                 | 21 |

| Figure 6.10 | Effect of Loop Construct Removal For Benchmarks.                                                                                                         | 22 |

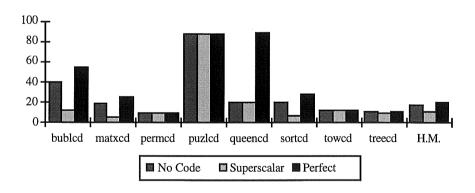

| Figure 6.11 | Effect of Memory Model on Performance                                                                                                                    | 22 |

| Figure 6.12 | Restrictive Memory Models                                                                                                                                | 23 |

| Figure 6.13 | Speculative Writes                                                                                                                                       | 24 |

| Figure 6.14 | Speculative Writes - With Procedure Ceilings                                                                                                             | 24 |

| Figure 6.15 | Varying Latencies For Model                                                                                                                              | 25 |

| Figure 6.16 | Results For Minimum Division Latency                                                                                                                     | 25 |

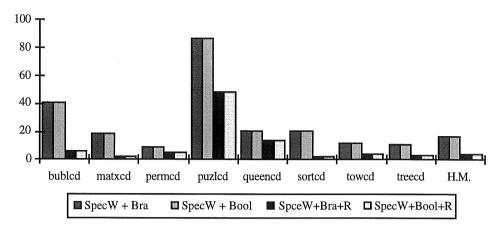

| Figure 6.17 | Combining HSA code.                                                                                                                                      | 26 |

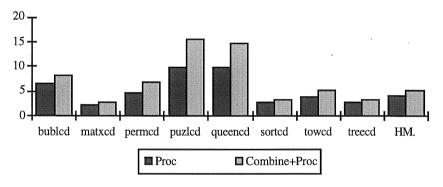

| Figure 6.18 | Combining With No Restrictions                                                                                                                           | 27 |

| Figure 6.19 | Combining With Procedure Ceilings                                                                                                                        | 27 |

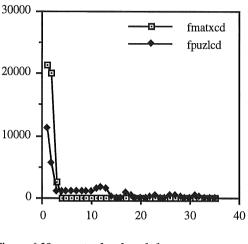

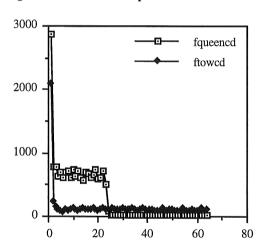

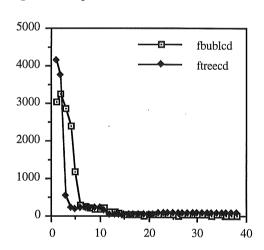

| Figure 6.20 | Distributions of Parallelism Figure 6.20a matxcd and puzlcd Figure 6.20b permcd and sortcd Figure 6.20c queencd and towcd Figure 6.20d bublcd and treecd | 28 |

## **List Of Tables**

| Table 2.1 | Limits of Instruction Level Parallelism       | 3  |

|-----------|-----------------------------------------------|----|

| Table 6.1 | The Stanford "Cut Down" Benchmark Suite       | 14 |

| Table 6.2 | Composition of Benchmarks by Instruction Type | 14 |

| Table 6.3 | Average Basic Block Sizes, Branch Distances   | 15 |

| Table 6.4 | Recursive Procedure Statistics                | 19 |

| Table 6.5 | Latencies Used                                | 25 |

#### 1. Introduction

In recent years there has been increasing interest in the use of compile-time instruction scheduling to improve the performance of superscalar processors [Bernstein92] [Smother93]. Instruction schedulers speed up program execution by assembling groups of independent instructions which can be executed in parallel at run time. Scheduling therefore involves moving or percolating each instruction up through the code structure to form these instruction groups.

Our research in this area is based on the Hatfield Superscalar Architecture (HSA), a generic superscalar architecture. HSA prefetches multiple instructions into an instruction buffer from the instruction cache. In each cycle, the instruction decode logic attempts to issue as many instructions as possible from the instruction buffer for parallel execution in multiple functional units. Ideally the instructions issued will correspond to the parallel groups assembled earlier by the instruction scheduler. Since code has already been reordered at compile time, the HSA instruction issue logic always issues instructions in order.

Numerous empirical studies [Lam92], [Smith89] and [Wall91] suggest that large numbers of instructions in a sequential program can theoretically be executed in parallel. For example, Lam and Wilson's study which aims to identify the upper limits of fine-grained parallelism, reported speedups of up to 158 using the SPEC benchmarks. In contrast existing instruction schedulers [Collins95] [Ebcioglu94] [Hank93] and [Wang93], typically achieve speedups in the range of 2 and 7. The speedup available in theory therefore exceeds the speedups achieved by existing instruction schedulers by over an order of magnitude. The objective of our research is to narrow this very significant performance gap.

Although notable performance improvements have been achieved, all instruction scheduling algorithms erect artificial barriers or as Wang [Wang93] called them, ceilings to code motion. For example, a particular algorithm may preclude the execution of any code within a loop body until all the code originally preceding the loop has first been executed. As a result of these ceilings, we have developed a Trace Driven Simulator (TDS), to quantify the instruction level parallelism in typical benchmarks and to relate the available parallelism to alternative instruction scheduling strategies. The results will be used to direct enhancements to the two HSA instruction schedulers which have been developed at the University of Hertfordshire. In particular, future work will be directed to removing those barriers to code motion which significantly limit performance, identified by the TDS tool.

This document is split into 7 main sections. The next section presents a summary of previous work in this field and discusses the major results presented so far. Section 3 introduces the Hatfield Superscalar Architecture and outlines its major features. Section 4 discuses some of the limits to instruction parallelism and those limitations introduced by various scheduling strategies. Section 5 outlines our approach to trace driven simulation. Section 6 presents a selection of the results so far generated. Finally, Section 7 presents the conclusions based on this study and further work suggested by it.

## 2. This Study and Previous Work

A number of researchers have attempted to quantify the limits of instruction-level parallelism (ILP) and their work has produced a large variety of results. This research has been approached in two distinct ways, either by proposing a feasible system design or by investigating the upper limits based on theoretical models, where many of the constraints have been relaxed other than those features under evaluation. Presented below is a discussion of some of these studies in chronologically order.

Early studies [Tjaden70], [Riseman72] showed that average parallelism within basic blocks rarely exceeded 3 on average. The study by Riseman was one of the first to show the effects of control flow on parallelism. By modelling a machine with foreknowledge of conditional branch direction, Riseman showed that a speedup of 51 was possible. Nicolau and Fisher [Nicolau84] referred to this as an Oracle machine. Nicolau's study was based on evaluating trace scheduling for a VLIW architecture. This work demonstrated that using a restricted processor model with perfect branch prediction and alias analysis, speedups of 90 were possible. Though these speedups were achieved using small scientific benchmarks where there is a large amount potential of ILP.

Smith et al [Smith89] used trace-driven simulation on a model of a realisable superscalar processor with multiple functional units. For a model with perfect renaming, branch prediction and an ideal fetch unit, speedups of between 2.3 and 4.1 were reported. However, several features of this study impeded the performance of the processor. Firstly, the issue rate was limited to 4 instructions per cycle, even though the processor had 9 functional units allowing a peak execution rate of 9 instructions per cycle (IPC). Secondly, the configuration of the functional units poorly matched the instruction class

execution frequency. In the study, 38% of the instructions executed were integer operations but the processor was resourced with only a single integer unit. The study noted that the biggest increase in performance occurred when a further integer unit was added. Finally, the processor had a very small look-ahead window of 32 instructions, which severely limits the ability of the processor to take advantage of the ILP present in the benchmarks. The study concluded that non-scientific applications contain enough instruction parallelism to sustain an instruction rate of two. This conclusion is only true based on the assumptions made within this study, for this one restricted design. This highlights the problems when attempting to quantify limits, that each reported limit is subject to all the limits and assumptions made within the study.

The work by Butler et al [Butler91] is a direct progression from the work of Riseman and attempts to refute the claims by Smith et al that the ILP within non-scientific code can only support an issue rate of two. Butler et al attempts to identify ILP for a range of unconstrained as well as realistic processor models. Butler's model used perfect branch prediction as well as unbounded functional units, issue rate and instruction window size. For an Unrestricted Dataflow model, parallelism in the range of 17 to 1165 IPC was shown for nine of the SPEC benchmarks. This study also placed limits on the extraction of ILP by assuming only one branch per cycle can be executed and no instruction following the branch can be executed in the same cycle. This limits the available parallelism to the average size of the basic block. Results for more realistic machine models suggest that, typically ILP inherent within non-scientific code ranges from 2.0 to 5.8 IPC.

A further study in this year by Wall [Wall91], concluded that even with impossibly good techniques parallelism rarely exceeds 7, with 5 more common. The most powerful model in this study had perfect branch prediction, jump prediction, register renaming and alias analysis. The extracted parallelism for this work was in the range 6.5 - 61. Wall's study had several features that limited the parallelism exposed to his models. Firstly, instruction execution is simulated by packing instructions from an instruction trace into a sequence of pending cycles. Each cycle could contain up to 64 instructions, limiting the maximum ILP to this figure. Secondly, in order to model a superscalars instruction window, the study's model only considers a constrained number of pending instructions. By default, this is 2k. Therefore, independent instructions more than 2048 instructions apart in the instruction trace will be prevented from executing concurrently. While 2k is an unrealistically large look-ahead window for a superscalar processor, it still confines the processor to realising parallelism from a very limited pre-fetch window of instructions.

Austin [Austin92] argued that 1st order metrics such as operation frequencies and branch prediction accuracies, were not sufficient to understand the characteristics of dynamic program execution for MII processors. To allow a thorough understanding of the interaction between operation dependencies, how these are impacted by the processor model and their effect on performance, the use of dynamic execution graphs were proposed. These graphs demonstrate how parallelism is distributed throughout the execution of the program. This work is modelled around the latencies of a MIPS processor<sup>1</sup>, to generate these graphs from an existing instruction trace. Using an Oracle dataflow model, parallelism was measured for the SPEC benchmarks and was found to range from 13 - 23,303. Optimistic assumptions about the usage of registers after system calls, increased the range to 33,748 IPC. More significantly, the distributions of parallelism were shown to be bursty, with areas of high ILP followed by areas of low ILP. The study concluded that a very extensive look-ahead window is needed, in excess of 100,000 instructions, to extract significant quantities of the available parallelism.

Lam and Wilson [Lam92] attempted to relax the constraints on control flow by using control dependence analysis, executing multiple flows of control simultaneously and using a speculative execution model. As in earlier studies, instruction execution was only constrained by true data dependencies and because an upper bound rather than a limit for a particular processor was being evaluated, unit latencies were used. However, the model used attempted to enhance the benchmark code by application of a perfect procedure inlining technique and loop unrolling. These mechanisms relaxed several limitations inherent in the code and exposed significant parallelism. The results ranged from 47 to 188,470 with a harmonic mean of 158.26.

As many of the benchmarks used in the above studies used the SPEC benchmark suite there is considerable overlap between the studies. Table 2 presents these results. It can be seen from this table that these 'limits' are directly affected by the assumptions used and by the architectures modelled. It can be concluded that there is adequate parallelism inherent in most programs to support an order of magnitude speedup through static instruction scheduling.

<sup>&</sup>lt;sup>1</sup> (Fp/Int Mult 6, Fp/Int Div 12, Fp Add/Sub 6, all other latencies 1)

| Benchmark  | Butler <sup>2</sup> | Wall <sup>3</sup> | Austin <sup>4</sup> | Lam <sup>5</sup> |

|------------|---------------------|-------------------|---------------------|------------------|

| Eqntott    | 300                 | _                 | 942.4               | 3282.9           |

| Espresso   | 179                 | 40.6              | 176.3               | 742.3            |

| Gcc (cc1)  | 38                  | 26.5              | 53.0                | 174.5            |

| Doduc      | 55                  | 56.8              | 107.2               | -                |

| fpppp      | 378                 | 60.4              | 2032.8              | -                |

| Matrix 300 | 1165                | -                 | 33748.6             | 188470           |

| Spice 2g6  | 17                  | -                 | 138.4               | 843.6            |

| Tomcatv    | 930                 | 59.7              | 6800.3              | 3918             |

| xlisp      | 162                 | -                 | 13.3                | _                |

Table 2.1 - Limits of Instruction Level Parallelism

This study is an attempt to find, for the benchmarks used within HSA, a reasonable upper bound on the available ILP. As the initial work on the HSA project has concentrate on a smaller benchmark suite, which are designed to be computationally intensive with unpredictable control flow, it will be extremely beneficial to place the results in context. Secondly, the majority of the processor models in the preceding work use superscalar out-of-order techniques, varying instruction latencies and branch prediction. The HSA project, as will be seen in a later section, is an attempt to minimise the hardware needed to issue multiple instructions in parallel by using static scheduling to re-order the code. The difference in techniques, mean that while the above studies provide useful guides to possible performance, they are not directly relatable. However, the principal aim throughout this study is to look at limitations to ILP, placed implicitly or explicitly on the execution model by scheduling algorithms. The effects of these limitations have not been studied so far.

## 3. Hatfield Superscalar Architecture

The Hatfield Superscalar Architecture (HSA) is a family of abstract Multiple Instruction Issue (MII) processors. The HSA is highly parameterised to allow investigation of hardware and software mechanisms to exploit instruction-level parallelism. The long term objective of the HSA project is to achieve an order of magnitude speedup over a scalar RISC architecture.

The HSA is often referred to as a minimal superscalar, as it is a progressive attempt to remove many of the mechanisms used within superscalar processors. The HSA does not support out-of-order issue, dynamic renaming or score-boarding and avoids branch prediction. Instead it by combines the best features of previous MII architectures, most notably Very Long Instruction Word (VLIW) processors and superscalar. Recent designs have shown that neither of these two methodologies have been sufficient to bridge the performance gap between what is theoretically possible and what has been realised. Both of these two distinct architectures have desirable features.

### **VLIW**

VLIW architectures have the advantage that no dynamic analysis is needed - the compiler performs any necessary analysis and schedules independent instructions into fixed length multi-operation instructions (VLIW's). The compiler can take a global view of the program and utilise sophisticated analysis techniques and code transformations that would be too expensive to perform at run-time. The use of instruction scheduling greatly simplifies the hardware required, leading to faster processor designs. However, schedulers for VLIW architectures [Ellis86] [Wang93] require the processor hardware to conform exactly to the assumptions built into the scheduler with respect to the number if functional units and operation latencies. Therefore the scheduled code is processor specific due to these rigid assumptions. A further problem is introduced by the fixed size of the VLIWs, the density of the schedule is dependent on the ILP present, if the scheduler cannot find sufficient independent instructions to fill the VLIWs, NOPS have to be inserted leading to code expansion problems.

<sup>&</sup>lt;sup>2</sup> Non Uniform Latencies

<sup>&</sup>lt;sup>3</sup> Unit Latencies

<sup>&</sup>lt;sup>4</sup> Mips Latencies

<sup>&</sup>lt;sup>5</sup> Unit Latencies

Superscalar

Superscalar processors are typically processors that analyse the instruction stream dynamically. In each cycle, every instruction within a given instruction window is analysed for dependencies. The processor takes a local view of program and reorders these instructions dynamically to exploit ILP. The hardware must therefore ensure all dependencies are detected and enforced. This dynamic analysis ensures code compatibility between processors and allows instructions to be considered across branch boundaries, for concurrent issue. The principal drawback with superscalar designs, is the hardware requirement to perform this dynamic instruction stream analysis and to ensure correctness of execution. The complexity of this hardware becomes prohibitively large at a moderate degree of parallelism. Existing designs have had difficulty dynamically analysing 2 to 4 operations, thus restricting the processors ability to exploit high ILP.

The HSA model attempts to combine these distinct designs by using compile time scheduling to reduce the hardware complexity, while maintaining code compatibility. The HSA removes the compatibility barrier for a static instruction scheduler by providing a generalised delayed branch mechanism. The use of this mechanism, allows the parallelism exposed by scheduling to be maintained when the code is converted back to sequential form, suitable for executing on a superscalar.

The HSA has the following major features; a generalised delayed branch, in-order instruction issue, out-of-order completion, conditional execution, a common pool of functional units, floating point capabilities, speculative execution and guarded instruction execution. Some of these features are discussed in the following sections:

#### 3.1 A Generalised Delayed Branch

HSA provides a delayed branch mechanism, that allows instruction execution to continue while a new instruction stream is fetched from the branch target. Branches have an explicitly encoded count value which indicates the number of instructions that must be dispatched after the branch. Instructions are then promoted to fill this branch delay region, including further branches. This flexibility allows the branch mechanism to adapt to a wide range of cache latencies and instruction issue rates, yet maintains instruction set compatibility over a range of implementations. This may have an impact on the overall speedup, if the processor the code has been scheduled for and the processor executing the code, are far apart in their ability to exploit the exposed parallelism. Results reported so far [Collins95], show that the reduction in performance is much smaller than would be expected. If code scheduled for a machine with infinite resources, is then executed on a machine whose degree of parallelism is only two, there is only an 18% decrease in performance. This result is based on a comparison with the figures for executing code scheduled for this 2-pipe processor. For a machine with a degree of parallelism of eight, this is reduced to only 6%. These results assume that the processor has the ability to squash instructions prior to dispatch.

#### 3.2 In-order Instruction Issue

In the HSA model, instructions are always dispatched in program order to the functional units, as sophisticated static code scheduling is used, making hardware re-ordering of the code redundant. By moving the responsibility for instruction analysis to the instruction scheduler, this has the advantage of avoiding a significant amount of hardware complexity in the instruction issue stage.

## 3.3 A Common Pool of Functional Units.

The HSA issues instructions to the appropriate functional unit from a common pool of resources from the instruction buffer. The number of functional units within the HSA model is not fixed, Arithmetic, Multiply, Memory Loads, Memory Stores, Branch, Relational, Shift and Floating Point functional units are postulated.

There is a trade off between the complexity of design for a large number of functional units and the usage of these resources. The greater the machine parallelism available, the greater the processor's ability to deal with areas of high ILP. Performance should not be greatly limited by instructions being 'blocked' from execution if there are not sufficient resources to handle it. Conversely, the number of functional units should not be unduly high, as the number of interconnections needed would require a very sizeable section of the chip area and there would be little to gain from a large number of lightly used functional units. This trade-off is not studied here, but further work on the configuration of functional units can be found in [Jourdan95] and [Collins95].

Three input operand functional units are provide in the HSA specification to allow combination of instructions. This allows combining of infrequently executed logic instructions with other operations in an attempt to avoid degrading ALU performance. A three input ALU unit may allow dependency chain to be compressed. The results of combining can be seen in this study in section 6.7.

## 3.4 Full Floating-Point Capability.

The HSA model fully supports floating-point instructions and has floating point versions of the relevant functional units. Floating point instructions would seem to further hamper performance as they have long instruction latencies associated with them. In HSA, as the scheduler has the ability to perform large scale code motion, it is thought that the floating point instructions with their long latencies will provide an extra boost to the exploitation of instruction-level parallelism. By allowing interleaving of the integer and floating point dependency threads, significant performance increases should be achievable over a scalar implementation of floating point HSA. Floating point capabilities also extend the usefulness of the processor itself, floating point resources can be used by both integer and floating point programs alike, allowing further improvement in performance on a range of applications.

## 3.5 Guarded Instruction Execution.

All HSA instructions can be guarded by multiple guard Booleans allowing conditional execution. For example consider:

FB1 ADD R1, R2, R3,

The ADD instruction will only execute to completion if its Boolean guard B1, evaluates to False at runtime. HSA attempts to 'squash' or remove instructions from the instruction buffer every cycle whose Boolean condition fails. The use of boolean guards helps improve resource utilisation by removing instructions prior to dispatch, therefore saving on functional unit, result bus and write back resource usage. Instructions can also be aborted within functional units allowing further savings.

An instruction scheduler can also use guarded execution to remove branch instructions by converting *if-then-else* constructs to a sequence of guarded instructions. These*if-then-else* constructs typically use conditional branches to select one of two short code segments. Booleans can be used to guard the subsequent *if* and *else* code elements, removing the need for a branch. Recent work has shown that this can reduce the number of dynamic branches dramatically; with the IMPACT group [Mahlke94] reporting a 27% reduction and Collins [Collins95] reporting a reduction of 35%.

#### 3.6 Speculative instruction execution.

To gain maximum performance, all instructions in the HSA instruction set, apart from Stores and Branches can exist in a non-speculative and speculative form. This allows instructions to be executed much earlier than their control dependencies would otherwise allow. Speculative execution allows instruction execution to proceed without waiting on the completion of previous instructions. This can have significant benefits, for example, a load instruction executed speculatively could allow other instructions dependent on its destination register, to begin execution much earlier. This could be especially critical on a slow cache machine or when loading from memory hierarchies. HSA handles the problems of exceptions in the presence of speculative execution by marking all registers with a flag indicating whether or not the register contents are polluted. Only when a non-speculative instruction attempts to access these polluted results will the exception finally be taken, thus allowing precise interrupts.

For a more detailed evaluation of the features of HSA see [Collins93] and [Steven95]

#### 4. Limits To Instruction-Level Parallelism

Instruction Level Parallelism (ILP) is a measure of the interaction between program parallelism and machine parallelism. Program parallelism is defined as the number of instructions a processor may be able to execute concurrently. Its is determined by the true data dependencies and control dependencies within the code. The latencies of the instructions determine how severely true data dependencies limit this program parallelism. Machine parallelism is a measure of the ability of the processor to exploit this program parallelism. Its is determined by the number of instructions the processor can fetch and execute at the same time. If the machine parallelism is smaller than the program parallelism, resource

conflicts will limit the processors performance. As these resource conflicts are not true limitations but are removable by duplicating contested resources, it is assumed in this study that machine parallelism is always sufficient. Therefore in this study, the available instruction level parallelism is determined entirely by program parallelism.<sup>6</sup>

The following sections describe the remaining limiting factors, data dependencies and control dependencies. They also explain how they each in turn limit instruction-level parallelism and ultimately performance. Also covered in this section, is the area of memory dependencies.

#### 4.1 Data Dependencies

There are five possible data dependencies between a pair of, three operand RISC instructions as used by HSA<sup>7</sup>. These are comprised of the three types of data dependencies that can limit the execution of the instruction pair.

Read-After-Write (RAW) or True dependencies occur when an instruction uses a value produced by a previous instruction. The second instruction is said to have a true data dependency on the first instruction and must be delayed until the preceding instruction produces the required result. Figure 4.1, shows two example HSA instructions, here the ADD requires the result of the preceding SUB instruction (R4) and is data dependent upon the SUB's destination register.

```

SUB R4, R9, R7 /* R4 = R9 - R7 */

ADD R5, R4, #28 /* R5 = R4 + 28 */

```

Figure 4.1 - Read After Write Dependency.

It is this prevention of execution of subsequent instructions that can have a critical impact on the execution of the program and severely limit the processors ability to execute more than one instruction per cycle. True data dependencies on long latency instructions can often prevent further instructions being executed leading to zero-issue cycles where no further instructions are executed. When the long latency instruction does finally complete, there is often only one new instruction that can be executed, thus creating a single-issue cycle due to the chaining of data dependencies through an instruction sequence. The number of zero and single issue cycles has a detrimental impact on the processors performance when executing a program. These true dependencies cannot be removed by instruction scheduling and ultimately limit the performance of all multiple instruction issue (MII) processors.

Write-After-Read (WAR) or Anti Dependencies occur when a register defined as a source operand for one instruction is also defined as the destination register for a succeeding instruction. The following instruction must be delayed to allow its preceding instruction to read the register before its is overwritten. In Figure 4.2, the register R6 cause the WAR dependency between the two ADDS.

```

ADD R4, R6, R8 /* R4 = R6 + R8 */

ADD R6, SP, #12 /* R6 = SP + 12 */

```

Figure 4.2 - Write After Read Dependency.

Write-After-Write (WAW) or Output Dependencies occur when two instructions specify a common destination register. This is show in Figure 4.3 where the two instruction both use R4 as their destination register.

```

SUB R4, R5, #2 /* R4 = R5 - 2 */

ADD R4, R6, R7 /* R4 = R6 - R7 */

```

Figure 4.3 - Write After Write Dependency.

Both WAR and WAW dependencies are a side-effect of the re-use of register and memory locations in the program; they cause a dependency between two otherwise independent instructions. These two dependencies are sometimes called Storage Dependencies to reflect this. Many of these false dependencies arise because compilers attempt to use as few registers as possible. In the case of

<sup>&</sup>lt;sup>6</sup> In the TDS tool, the processor is modelled as having infinite resources.

<sup>&</sup>lt;sup>7</sup> HSA instructions are typically of the form:-

<sup>&</sup>lt;opcode><destination><source register1> <source register2>

registers, storage dependencies can be removed by using a different register for the second result. In Figures 4.2 and 4.3 renaming R6 and R4 respectively, will remove the dependencies.

It is important to distinguish True dependencies from these storage dependencies, as this type of dependency represents the flow of data and information through the program and therefore cannot be eliminated readily.

#### 4.2 Control Dependencies

Control Dependencies or procedural dependencies, are introduced as a result of control flow within the dynamic instruction stream. If a processor has foreknowledge of all the instructions that will be executed (this type of machine is often referred to as an *Oracle*) it has been shown that it can achieve dramatic speedups [Lam92]. Unfortunately because of branches in the dynamic instruction stream, the processor only discovers which instructions are executed as the program is executed. For every branch taken, the branch target must be resolved, instructions must be fetched from the branch target stream and any unwanted instructions removed from the instruction buffer. Therefore every execution of an instruction, has a control dependency (sometimes called a procedural dependency) on the immediately preceding branch. The average number of instructions between branches is usually small; Johnson [Johnson91] reported an average of 6. If substantial ILP is to be realised, the effects of these control dependencies can be reduced by speculatively executing instructions along one or more paths before all the preceding conditional branch instructions have been resolved. Lam's study showed a harmonic mean for the speedup of an oracle model of around 158. For a similar processor model using good branch prediction the results were less encouraging, Wall's study reported speedups in the range of 4.1 to 7.4. This suggests that control flow is indeed a major inhibitor to performance.

## 4.3 Artificial Limitations To Code Motion

As well as the limitations inherent within the code, instruction scheduling algorithms also introduce restrictions on instruction execution and code motion, which in turn limit the speedups realised. These barriers may be introduced as side-effects of an algorithm or may be explicitly dictated by the algorithm. In either case they may significantly limit the amount of ILP realised. Three major areas are considered in this study where these barriers have a significant impact: loops, procedure calls and memory disambiguation. Further work is also carried out to study the effects on instruction combining and the impact of allowing speculative writes.

### **4.3.1 Loops**

In may programs a significant proportion of the execution time is spent in loops. Therefore instruction schedulers attempt to optimise these loops as way of optimising a major part of the execution time, concentrating on generating efficient schedules for inner loops and on minimising the initiation interval between successive iterations. The minimum loop iteration rate cannot be lower than the longest latency instruction within the loop.

As long as a loop body is not duplicated or unrolled, the iteration interval can also never be less than the minimum number of cycles required by the processor to execute a tight loop. In a machine with dynamic branch prediction hardware, this minimum can be a single cycle. However, in a machine like HSA with a delayed branch mechanism, the minimum iteration interval may be two or more cycles depending on the minimum number of branch delay slots. An alternative way of viewing this lower limit is to observe that there must always be a minimum delay before an instruction within a loop can be re-executed.

Loop iteration intervals are also dictated by loop carried dependencies, where an instruction in one iteration uses a result generated in a previous iteration. However, many of these dependencies are introduce by loop indices. These are spurious dependencies and are not an intrinsic part of the loops processing. For example, the final result of incrementing index i ten times in ten successive loop iterations can be collapsed into a single addition of ten. The TDS tool examines the effect of combining successive calculations involving literals, effectively collapsing all dependencies involving loop indices.

Another side effect introduced during loop scheduling is that code within the body of the loop is only executed after all the instructions preceding the loop have been executed. This delays the effective starting time of the loop's execution and prevents parallel execution with other code. In particular, two

independent loops can never execute in parallel. The impact of this is modelled along with studying the effects of code motion across loops and the effects of code motion into loops.

The final limitations studied are the barriers introduced by the compiler as it generates code for the loop. As most compilers generate code for scalar machines, they produce unnecessary serialising components. These components are not an inherent part of the loop semantics and the effects of their removal are also studied here. These limiting factors include the incrementing of the loop index, as discussed above, comparisons based on the loop indices and branches based on the result of these comparisons.

#### 4.3.2 Procedure Call and Returns

As the concept of modularity increases within applications (especially due to the prevalence of object orientated techniques) the impact on performance of procedure calls and returns will be significant.

Instructions within a procedure are typically never issued until all the instructions in the calling procedure are issued. The same is true for the return from a procedure, where the instructions after the return have to wait for the instructions in the procedure to complete. This imposes a further barrier to ILP. In the Stanford benchmark suite used in this study, procedure entry and exit calls typically accounts for 26% of all branches. The impact of inlining of recursive calls and motion across the procedure are investigated to asses their impact on reducing the impact of these ceilings. Recursive procedure calls are treated as loops, by selectively removing the ceiling associated with procedure entry for directly recursive loops and by partial collapsing of the associated stack frame.

The procedure construct also introduces unnecessary serialising constructs which are added during compilation. A new stack frame is allocated and deallocated for each procedure introducing dependencies on the stack pointer (SP), and a significant amount of memory traffic is generated saving and restoring registers across procedure calls. For a program with many small procedures this will have a major impact on the ability of a scheduler to take advantage of the available parallelism. To reduce these barriers, the use of selective and perfect procedure inlining is studied.

#### 4.3.3 Memory Dependencies

HSA, like other RISC architectures limits memory access to load and store instructions only. To take advantage of any parallelism present in the code, a compiler/scheduler for HSA needs the ability to perform large scale code motion. This will often involve the reordering of memory references. This problem is compounded further, due to the large difference in processor speed and memory speed for many architectures, resulting often in long instruction latencies. This implies that to avoid problems associated with these long latency instructions, we have to execute multiple memory accesses in parallel and or out of order. The memory address therefore require aliasing or disambiguation to find those access which are independent and that can therefore be executed safely in parallel.

Because the addresses of the memory locations being accessed are not always available at compile time, the address are calculated from values held in the registers at run time,. The scheduler has to take a conservative approach and execute memory access in the sequential order of the code. This is the only safe assumption it can make, for example in Figure 4.4, unless the scheduler has the ability to ascertain that the references in I1 and I2 cannot refer to the same memory location. In Figure 4.4 this would mean writing to address 1 and then loading from address 2. It may be more beneficial to execute the load from address 2 and then write to address 1 as the load will free up further dependent instructions. However, this would result in the wrong value being read if it address 1 = address 2.

```

I1 ST (R9, R10 /* address 1 */), R11 ....

I2 LD R4, (R7, R8 /* address 2 */)

ADD R6, R5, R4

```

Figure 4.4 - HSA Memory Reference

The HSA scheduler would have to perform its disambiguation statically. Address 1 for example, is calculated by adding R9 to R10 and address 2 by adding R7 to R8. As these addresses are calculated from values held in the register file they cannot be distinguished at compile/schedule time and would have to executed in order. Static disambiguation techniques are only effective when the memory access patterns are linear and predictable, which is often not the case in general purpose code. Targeting loops is one way to combat the problem, as most memory operations often involve array accesses. Even so

this form of static disambiguation involves solving complicated linear diophantine equations, may require the loop bounds which are often not available and it cannot cope very well with pointer dereferencing.

A central point of this research is to examine the effect of memory disambiguation with respect to the scheduling algorithms used in the HSA scheduler.

The impact of speculative writes is also assessed within this study. Unguarded writes can only be fetched as soon as the preceding control-flow has been resolved. Even if the write is guarded it can only be executed once the branch condition has been resolved. These restrictions could limit performance if the store blocks the motion of subsequent loads. This will occur when memory disambiguation fails.

### 5. Trace Driven Simulation

## 5.1 Overview of Simulator Model

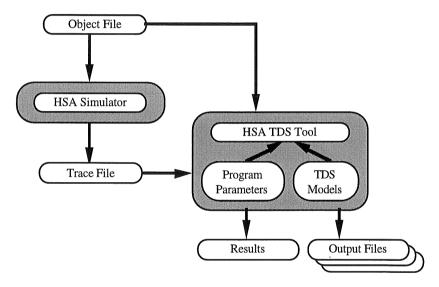

The HSA TDS tool was developed to quantify the available parallelism in typical benchmarks and to study the effects of the code ceilings introduced. All simulations are performed as shown in Figure 5.1.

Figure 5.1 Flowchart of Trace Driven Simulation

The optimised object code for the benchmark under evaluation, is first executed on the HSA simulator [Collins93], which generates a compact trace of taken branches and load/store addresses. This trace provides all the relevant information to perform trace driven simulation and considerably smaller than a full instruction trace. Even so, the size of these trace files can reach 2Mb for the full-length versions of the benchmarks used in this study. This dynamic trace stream and the original object code are then loaded into the HSA TDS tool. The TDS tool simulates the execution of the object code based on a model of the execution being tested. Various parts of the model can be activated or deactivated to allow studying of individual and combined effects.

Each instruction as it is examined, is allocated a Parallel Instruction Time-slot (PIT), which indicates the earliest time at which the instruction could be executed. The TDS tool determines for each instruction, when the source operands including memory locations, will be available. The PIT time of the source operand that was computed last is then added to the latency of the instruction to create a new PIT, which is then associated with the destination register.

Instructions arbitrarily far apart in the original code can therefore be allocated the same PIT number, indicating that they could have, theoretically been executed in parallel. The largest PIT created by the program is then taken as the total execution time for the benchmark.

No instruction can be executed before its input operands are available.

```

1. Instruction To Execute :

1

L6:

ASL

R4

R6

Checking Source Operands For Instruction:

R6. 1

Pit That Instruction Can Be Executed In = 1

2. Instruction To Execute :

17

1

ADD

R5

R7

R4

Checking Source Operands For Instruction:

R4. 2

R7, 1

Pit That Instruction Can Be Executed In = 2

```

Figure 5.2 - Sample Breakpoint File From permed

Figure 5.2 is a sample trace of a TDS breakpoint trace file. The first instruction, ASL (arithmetic shift left), has its source operands checked, in this case R6 which is shown to be available in PIT number 1. The shift instruction is allowed to 'execute' in this time-slot and the destination register R4 is associated with the latency of this instruction and this PIT. This can be seen in the ADD instruction which has R4 as a source operand. R4 is checked and is shown to be available next in PIT 2. As this is the latest operand for the ADD instruction, this is the also the time-slot that the instruction will be allocated.

The TDS tool strictly enforces all true data dependencies, as shown above with R4. In contrast antidependencies and output dependencies are effectively ignored. Since both these dependencies can be removed by renaming, the TDS tool effectively assumes perfect renaming of both register and memory locations.

The TDS tool has perfect knowledge of all memory addresses accessed by the program under simulation and is therefore able to simulate perfect memory disambiguation. This simple execution model with many of the restrictions on execution relaxed is used to compute the upper bounds of the available instruction-level parallelism and is equivalent to the Oracle model used in other studies. Additional restraints are then introduced to the model allowing the TDS tool to quantify the impact of restrictions introduced by instruction scheduling algorithms.

## 5.2 Representing Programs Within TDS

## **5.2.1 Principle Parameters**

The TDS tool has a high level of parameterisation, allowing individual components of the tool to be switched on or off, to allow the study of a single effect or the combination of several models and parameters. The TDS tool parameters are grouped around 6 main groups: viewing of data structures and results, simulation, instruction latencies, code alterations, memory and breakpoints.

The TDS tool has facilities for viewing the structures used within the TDS to model caches and the program under test, allowing the user to study the information held in the tool; viewing of the instruction cache, procedures in the current program, the basic blocks that make up the procedures, the current symbol table, distributions of parallel instruction time slots are a few of these.

The simulation group of parameters control the 'execution' of the program and allow the user to specify what output is produced by the TDS tool. Ceilings to code motion can also be set here, these include; entrance and exits to loops, procedure calls and returns and allowing specific code motion across the ceilings.

The TDS tool has a number of predefined latency groups, the HSA latency set, a Unit latency set and set of long latencies based on the Cydra 5 machine. The user can also set individual latencies for all the principle instruction types within given limits. For Branch and Stores these limits are between zero and ten. Loads can be set with latencies up to twenty six to allow the simulation of very slow memory accesses or from cache hierarchies. Division latencies can be set as high as forty cycles to emphasise

the effects of very long instruction latencies. The other main instruction types are Multiplication and Arithmetic, which are allowed latencies up to and including twenty five and twenty, respectively.

The TDS tool also allows manipulation and alteration of the original program code. Under the code alterations menu the tool allows inlining of specific procedures, loop un-rolling, simulation of perfect inlining and combination of instructions. Some of these operations alter the code and place new copies of the code back into the instruction cache. These options cannot restore the code back to its original state without re-loading and should be used with caution.

The final set of parameters allows various methods of memory disambiguation to be selected for modelling. These range from perfect memory disambiguation through more restrictive models, to no disambiguation and allow the impact of the memory disambiguation techniques to be studied. This group also allows ceilings to placed on the memory references preventing them from executing out-of-order, or speculatively before the preceding branches have been resolved. Further restraints can also be placed preventing memory references from moving across procedure calls or out of their associated basic blocks.

The facilities offered by breakpoints will be covered in Section 5.6, Tracing facilities.

#### 5.3 Loading the TDS Tool

## 5.3.1 Loading The Instructions

The TDS tool allows object files to be selected and loaded into the TDS tool. The traces used for simulation require that the instructions be held in an instruction cache that matches that of the HSA simulator to ensure that the cache addresses given in the trace file will be identical. The instructions are read in a line at a time from the object file, each line is identified, decoded and placed in an instruction record. Each record contains fields to hold the primary components of each instruction including attached labels, types, op-codes, destination operands, source operands and branching information. Any labels in the code are collected as the instructions are loaded and placed in a general symbol table.

Once the main instruction file is loaded, the general symbol table is scanned for known library calls. Any libraries identified are then also loaded. Currently the only standard C libraries supported by the TDS tool are printf and malloc, which contain instructions to make the appropriate system calls. These are again included to maintain a consistent model with the HSA simulator. As the object code is designed to be re locatable, all the branch target labels are then placed within the symbol table and the branch targets of every branch instruction can be then altered to map the branch target label to the correct instruction.

## 5.3.2 Data Items

As the TDS tool is not required to model and simulate a data cache, all data items, both initialised and uninitialised are collected and placed in a temporary data structure. These labels are then placed into the general symbol table to allow the TDS tool to display and identify them easily. As well as being placed into the symbol table, the data labels are placed directly into the memory map which is used to associate an availability time with each memory location so that memory references can be handled as operands.

#### 5.4 Main Simulation Loop

The TDS tool performs most of its work within a main simulation loop. This loop controls and checks the processing of each instruction and the collection of information about the program under simulation. Although fairly complex, the loop consists of a number of distinct stages; loading from the trace file, using the trace file to step through the instruction cache, checking operand availability for each instruction and allocating an execution time, checking for ceilings and breakpoints.

#### **5.4.1 Trace Files**

The TDS tool requires for each simulation a trace file of each benchmark executing on the HSA simulator, these can be generated on request. An Example of such a trace is given in figure 5.3.

| В | 2  | 127  | S | 128 | 3968 | В | 129 | 89   | S | 90 | 3840 | S | 91 | 3848 |

|---|----|------|---|-----|------|---|-----|------|---|----|------|---|----|------|

| S | 92 | 3852 | S | 93  | 3856 | В | 94  | 4    | S | 6  | 5568 | В | 8  | 95   |

| В | 96 | 18   | S | 19  | 3712 | S | 20  | 3720 | S | 21 | 3724 | S | 22 | 3728 |

| S | 23 | 3732 | В | 33  | 9    | L | 10  | 5568 | S | 14 | 5568 | В | 17 | 34   |

| S | 43 | 4164 | В | 46  | 33   | В | 33  | 9    | L | 10 | 5568 | S | 14 | 5568 |

Figure 5.3 - An example section of a trace file

The trace file consists of all the branches taken and memory references used by the program. The characters in the trace indicate the type of the instruction, 'B' for a branch, 'L' for a load and 'S' for a store. For a branch, the first number is the address of this branch in the instruction cache and the second number is the branch destination address within the instruction cache. This information is recorded into the trace when the program counter is physically altered in the branch unit of the HSA simulator. For a memory reference the first figure is again the current instruction cache address and the second is the effective address for the memory access. This information is recorded into the trace when the instructions are issued. All the traces files were generated on the single pipe model allowed by the simulator.

The TDS tool reads a line at a time and separates the line into a sequence of tokens, these tokens are then used to control the simulation.

# 5.4.2 Simulating the 'Execution' of a Benchmark

The program is assumed to begin executing at instruction cache address zero. The instruction at the current program counter is identified and a specific handling routine for each instruction type is called. Each source operand is checked, the latest operand time is associated with the instruction and a destination time is associated with any destination operands. For each instruction type that does not require information from the trace file, this will be as shown in Figure 5.2. At this stage it is assumed that any ceilings being modelled, have effected the operand availability times or the execution time of the instruction. A simplistic model of this is presented in the following section (5.4.3) and further information is given for each simulation model when its results are presented.

For branches and memory references a slightly different sequence of events is initiated. Branches are not guaranteed to appear in the trace file, they are only placed in the trace file by the HSA simulator, if they are taken. For the Stanford benchmarks used, the figure for branches not taken is around 25%. The TDS tool firstly checks if a branch is the next instruction it expects to see in the trace file. If so the current program counter is checked against the branch instruction address read in. If these match, the branch is taken and the program counter is adjusted to the branch target address, this new program counter is checked against the read in branch target cache address, to ensure correctness. The TDS tool has to also handle branches not appearing in the trace file and branches not matching in the trace file. In both of these cases it has to assume that the branch under examination is not taken and execution should continue at the branch's sequential successor.

Memory Loads and Stores, as well as providing effective addresses for memory references, are used to check the simulation is executing as expected. These instructions will be examined by the TDS tool in the same order as they were executed in the HSA simulator, the information they convey is used to maintain simulation correctness. The effective address read in are used to perform memory disambiguation within TDS. Each effective address is placed within a memory map and has the time of the memory reference associated with it. All memory references are checked against this memory map.

The TDS tool will continue stepping through the instruction cache until all the trace file has been processed and further instructions require trace file information, in which case an error has occurred, or until a TRAP instruction is executed, indicating the successful completion of the program.

#### 5.4.3 Ceilings and Breakpoints

In addition to the instructions held in the instruction cache, the TDS tool also has a further data structure which models the program, its procedures and their associated blocks. The program is modelled as a complex data structure, but at the top level it can be reduced to a program name and a list of procedures. The procedures consist of pointers to further procedures, pointers to the instructions that make up the procedure via basic blocks and a back edge list for all the loops in the procedure. This higher level information allows the TDS tool to keep track of specific events, such as loop entrance and loop exits. Which, with the use of global ceiling variables, can be used to set ceilings for code motion

that effect all the other procedures that implement the simulation. These ceilings can be for all instructions or for a selected specific type of instruction, most commonly memory references.

The TDS tool allows various trace methods to be used during the simulation. By far the most useful of these traces is the one controlled by breakpoint information. This allows breakpoints to be created for specific instruction counts or instruction cache addresses. When a breakpoint is encountered, the options to remove the breakpoint, trace a specific number of instructions, trace a specific number of branches and memory references, examine the memory map and examine register usage at this point are presented to the user. This allows valuable information to displayed in a controllable way. Tracing instructions shows which ceilings are being implemented, the availability of operands and the allocation of PITs to instructions as well as further information regarding register usage. This feature was used to debug the TDS tool and is left in as it provides an in-depth and useful tool to examine exactly what is happening and in what order at any stage. As yet there is no facility to enter the trace mode when an error occurs. This feature has been omitted because any errors that occur within the TDS tool are likely to be fatal errors. These errors are likely either to be a problem with the implementation or user error. Simple user error is the most common form, typically using object files and trace files that do not match.

Further trace facilities are available to the user. Outputting the trace file to a given file can be selected, presenting a more condensed form of the trace information. A tuple output file can be generated, this is contains highly condensed output, consisting of a collection of instruction cache addresses and their associated PITs. A branch error file can also be selected, storing information for all the branches not taken,. These outputs are a representative sample of the TDS tool outputs.

## 6. Results

This section presents the results of removing many of the constraints placed on executing code sequences, to allow us to quantify the amount of ILP in non-numeric code. The effects of placing barriers to code execution and the impact they have on the available ILP are also presented. The results are displayed in terms of the speedup of a suite of benchmark programs running on the TDS tool compared to the same programs executing on a single pipe HSA model. Speedup is defined as the number of cycles taken by a scalar processor to execute the program divided by the number of cycles taken by a superscalar processor to execute the same program. The results obtained are then analysed to assess the cost, in terms of performance and impact on the available ILP, of these constraints, both as singular effects and as combinations of constraints. The full set of results are available in Appendix A.

## 6.1 Benchmark Programs

For this implementation of TDS, the small integer Stanford benchmark suite was selected. This collection of eight 'C" programs was designed by John Hennessey, to be representative of non-numeric code while at the same time being compact. The benchmarks are computationally intensive with high dynamic instruction counts. Under test, they perform very much like larger benchmark suites. All the benchmarks were compiled by the HSA gnu 'C' Compiler which targets the HSA instruction set. For this initial study, 'cut-down' versions of the benchmarks where used. The primary reason for using these cut-down versions was the ease of testing and debugging with the smaller dynamic instruction counts and also to avoid generating large trace files until TDS was more stabilised. These cut-down versions (indicated by a "cd" suffix on the benchmark names), still implement exactly the same algorithms as the full length versions but work on reduced problem sets, thus keeping most of the desired properties.

As shown in Table 6.1 each of the benchmarks consist of a small number of procedures (the average size is approximately 8). Each procedure has an average basic block size of around four instructions. Three of the benchmarks *permcd*, *towcd* and *treecd*, are highly recursive with a large number of procedure calls being made throughout the execution of the program. The average percentage of total instructions that are branches for these three benchmarks is about 17%, of which 54% are procedure call and returns. In contrast *bublcd*, *matxcd*, *puzlcd* and *queencd* spend over 80% of their time executing within loops. An average of 50% of the total number of lines in these benchmarks accounts for 88.4% of the total execution.

| Program | Num.<br>Procs | Lines | Basic<br>Blocks | Avg Size<br>Of Block | Description                                                   |

|---------|---------------|-------|-----------------|----------------------|---------------------------------------------------------------|

| bublcd  | 7             | 106   | 28              | 4                    | Bubble Sort an array of 50 Integers                           |

| matxcd  | 7             | 133   | 24              | 6                    | Multiplication of two 10 by 10 integer matrices.              |

| permcd  | 7             | 97    | 25              | 4                    | Recursive computation of all the permutations for 5 elements. |

| puzlcd  | 8             | 589   | 145             | 4                    | Recursively solves a cube packing problem.                    |

| queencd | 6             | 164   | 33              | 5                    | Recursive solution of the eight queens chess problem.         |

| sortcd  | 8             | 145   | 35              | 4                    | Recursive quicksort of 100 elements.                          |

| towcd   | 12            | 222   | 47              | 5                    | Solves the tower of Hanoi problem for 7 discs.                |

| treecd  | 11            | 219   | 54              | 4                    | Performs a binary tree sort of 100 elements.                  |

Table 6.1 - The Stanford "Cut Down" Benchmark Suite

Four of the benchmark suite, bubled, matxed, sorted and treed, contain a mixture of Multiply and Divide instructions. Although these represent a small proportion of the dynamic instruction count, (the percentage of the dynamic composition for these instructions is 2% and 0.5%, respectively) the long latency of these instructions may seriously limit the potential for parallelism, by delaying subsequent instructions in the long dependency chains that exist in the benchmarks.

All the cut down benchmarks execute under 40,000 instructions, which means that while the individual speedups achieved are individually meaningless, useful interpretations can still be drawn by comparison across a range of results.

## 6.1.1 Composition of the Benchmarks

| Program | St   | %      | Ld   | %      | Arith  | %      | Mult  | %      |

|---------|------|--------|------|--------|--------|--------|-------|--------|

| bublcd  | 1377 | (8.8)  | 2801 | (18.0) | 4334   | (27.9) | 100   | (0.6)  |

| matxcd  | 1516 | (5.9)  | 3215 | (12.6) | 10760  | (42.1) | 1200  | (4.7)  |

| permcd  | 1723 | (20.1) | 1716 | (20.0) | 3192   | (37.2) | 0     | (0.0)  |

| puzlcd  | 2304 | (6.5)  | 2876 | (8.1)  | 12180  | (34:5) | 0     | (0.0)  |

| queencd | 3157 | (14.7) | 3796 | (17.6) | 5631   | (26.1) | 0     | (0.0)  |

| sortcd  | 939  | (7.1)  | 2044 | (15.5) | 4093   | (30.9) | 200   | (1.5)  |

| towcd   | 2892 | (18.0) | 3235 | (20.1) | 5808   | (36.1) | 0     | (0.0)  |

| treecd  | 2193 | (9.2)  | 5103 | (21.4) | 7985   | (33.6) | 200   | (0.8)  |

|         |      |        |      |        |        |        |       |        |

| Avg.    | 2013 | 11.3   | 3098 | 16.7   | 6748   | 33.6   | 213   | 0.95   |

|         |      |        |      |        |        |        |       |        |

|         | Div  | %      | Bool | %      | Branch | %      | Shift |        |

| bublcd  | 50   | (0.3)  | 2698 | (17.4) | 2808   | (18.1) | 1373  | (8.8)  |

| matxcd  | 200  | (0.8)  | 1330 | (5.2)  | 1940   | (7.6)  | 5390  | (21.1) |

| permcd  | 0    | (0.0)  | 420  | (4.9)  | 1314   | (15.3) | 212   | (2.5)  |

| puzlcd  | 0    | (0.0)  | 6084 | (17.2) | 6559   | (18.6) | 5347  | (15.1) |

| queencd | 0    | (0.0)  | 3512 | (16.3) | 3849   | (17.9) | 1604  | (7.4)  |

| sortcd  | 100  | (0.8)  | 1701 | (12.9) | 2392   | (18.1) | 1760  | (13.3) |

| towcd   | 0    | (0.0)  | 794  | (4.9)  | 2429   | (15.1) | 922   | (5.7)  |

| treecd  | 100  | (0.4)  | 2437 | (10.3) | 5123   | (21.6) | 595   | (2.5)  |

|         |      |        |      |        |        |        |       |        |

| Avg.    | 56   | (0.3)  | 2372 | (1.1)  | 3302   | (16.5) | 2150  | (9.6)  |

Table 6.2 - Composition of Benchmarks by Instruction Type

Table 6.2 gives a distribution for each instruction type for the benchmark programs based on the dynamic instruction count. If shift, multiplication, divide and arithmetic instructions are grouped together to form a super-group of ALU operations, these comprise 44.5% of all the operations executed. This figure compares favourably with those reported by Gross [Gross88] for the MIPS instructions set usage, where ALU operations typically consisted of between 40-50% of all operations.

This is also true of loads and stores within the benchmarks which comprise 28% of the total, Gross reported that loads and stores instructions are between 25-30% of the total. The MIPS work was performed on the full length versions of the Stanford benchmark set and several much larger benchmarks. Typically these benchmarks running for millions of instructions and this shows that the "cut-down" Stanford set of benchmarks compare favourably. Although, some studies have shown that small integer benchmarks do not contain many pairs of ambiguous memory references, this was not found in this initial study.

#### 6.1.2 Branch Instruction Profile

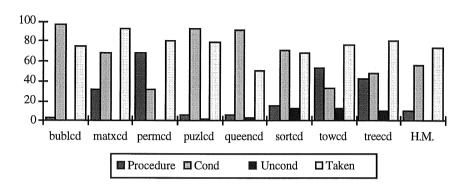

Figure 6.1 - Distribution of Branch Types and Branch Taken Figures.

Figure 6.1 gives the distribution of branch types for the Stanford cut-down benchmarks, in terms of the percentage of branches that where procedure calls and returns (Procedure), conditional (Cond) and unconditional (Uncond). The high proportion of conditional branches in the benchmark suite is a good representation of the complex dynamic control flow which is typical of non-numeric code. A further good indication is that of branches taken. Although in some benchmarks, notably matxed, a high proportion of all branches are taken, the harmonic mean is around 73%, leaving 27% of branches untaken. This figure correlates to the figures reported by Gross [Gross88] in which taken branches are less than 20% of the dynamic instruction count. Based on the harmonic means, taken branches are around 12% of this count for the cut-down benchmarks.

## 6.1.3 Basic Block Statistics

| Benchmark | Static<br>Average | Dynamic<br>Average | Avg. Branch<br>Distance |

|-----------|-------------------|--------------------|-------------------------|

| bublcd    | 3.8               | 4.5                | 5.5                     |

| matxcd    | 5.5               | 12.3               | 13.1                    |

| permcd    | 3.9               | 6.1                | 6.5                     |

| puzlcd    | 4.1               | 5.0                | 5.4                     |

| queencd   | 5.0               | 5.4                | 5.6                     |

| sortcd    | 4.1               | 4.7                | 5.5                     |

| towcd     | 4.7               | 6.3                | 6.6                     |

| treecd    | 4.1               | 4.5                | 4.6                     |

Table 6.3 - Average Basic Block Sizes, Branch Distances

Table 6.3 presents the average basic block size for each program. The dynamic average is calculated by dividing the total number of instructions executed by the total number of basic blocks. The table also presents the average distance between branches of each program. This distance is defined as the total number of instructions between branch instructions, including the branch instruction itself. This is related to the average basic block sizes but not identical because basic blocks need not be separated by a branch instruction.

Figure 6.2 - Dynamic Run Length Distribution of Taken Branches

For general purpose code, the instruction runs are quite short. Figure 6.2 shows the distribution of run lengths for the Stanford benchmarks. The run-length is determined by the number of instructions between taken branches. Branches not taken are counted as part of the run and every time a branch is taken a new run length count is started. This is measured as the program execution is simulated by the TDS tool and the output is optional. The average run length for the Stanford suite is around 6, but this is aided by the large number of run lengths of eight instructions or more. The size of these run-lengths has a critical impact on instruction fetching.

Harmonic means (H.M.) are used throughout this study as well as arithmetic means to avoid distortion in the reported speedups by applying larger weightings to the programs reporting the smaller speedups.

For a set of N programs, each with a speedup  $S_n$  the harmonic mean of all speedups is: Harmonic Mean = N /  $(\sum_{N} 1/S_n)$ .

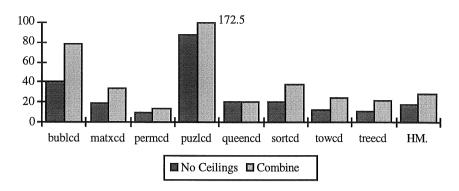

The effects of this distortion can be seen in a number of the results reported. For example figure 6.3, *puzlcd* has a considerably greater speedup than any other of the benchmarks, the arithmetic mean reported here is 35.1 but the harmonic mean is only 21.5. The arithmetic mean does not accurately reflect the speedups for the whole benchmark suite and is presented to allow comparisons only.

#### **6.2** Oracle Base Model

As a base model for comparison, the TDS tool initially ran the benchmark programs with no constraints being modelled. This Oracle model represents a processor with perfect memory disambiguation, infinite resources and perfect branch prediction. Therefore the execution time of each program is dependent on the true data dependencies (which represent the flow of data and information) present in the programs only.

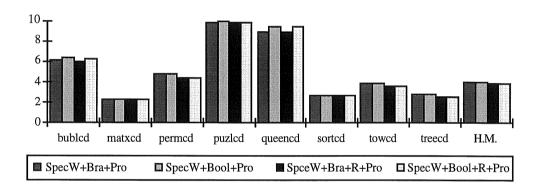

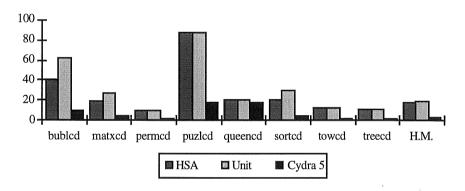

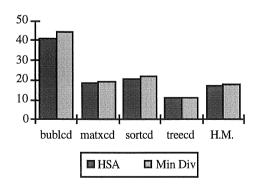

Figure 6.3 - No Ceilings Modelled